简介

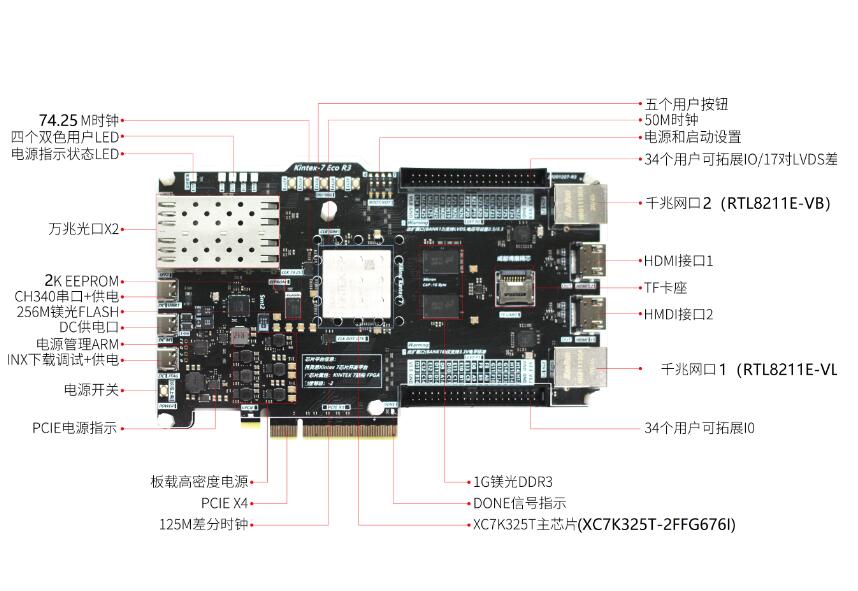

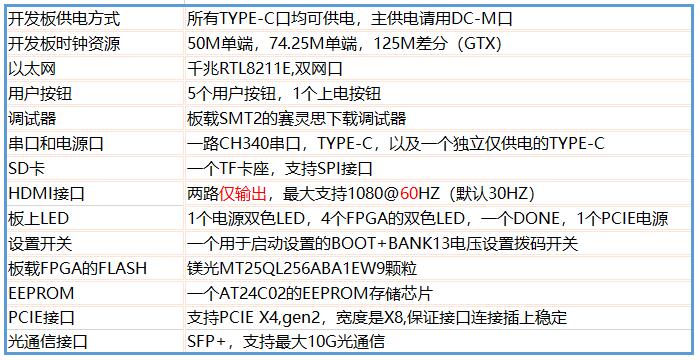

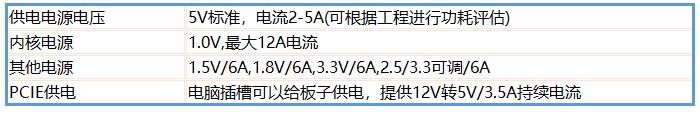

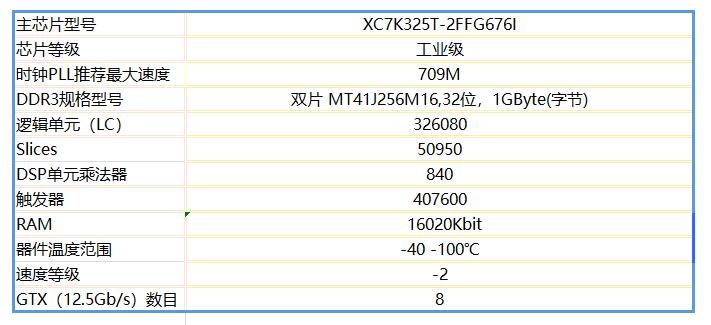

手上的有一块小熊猫嵌入式电子的7k325T FPGA,这里记录的是一些常用信息,以便查阅。

Vivado板卡

相关硬件

配置文件固化FLASH-MT25QL256ABA1

在工程设置中,勾选生成bitstream时生成bin文件

在约束文件中添加

set_property BITSTREAM.CONFIG.CONFIGRATE 33 [current_design]

可以提高SPI工作频率频率,加快上电配置速度,33代表33MHz

在硬件管理页面,设置FLASH固化型号,并固化

2片DDR,16bit*2-MT41J256M16

引脚配置文件DDR3_PIN_OUT.ucf

NET "ddr3_addr[0]" LOC = "AF8" | IOSTANDARD = SSTL15 | VCCAUX_IO = NORMAL;

NET "ddr3_addr[10]" LOC = "AC9" | IOSTANDARD = SSTL15 | VCCAUX_IO = NORMAL;

NET "ddr3_addr[11]" LOC = "Y11" | IOSTANDARD = SSTL15 | VCCAUX_IO = NORMAL;

NET "ddr3_addr[12]" LOC = "V9" | IOSTANDARD = SSTL15 | VCCAUX_IO = NORMAL;

NET "ddr3_addr[13]" LOC = "V7" | IOSTANDARD = SSTL15 | VCCAUX_IO = NORMAL;

NET "ddr3_addr[14]" LOC = "Y7" | IOSTANDARD = SSTL15 | VCCAUX_IO = NORMAL;

NET "ddr3_addr[1]" LOC = "AA10" | IOSTANDARD = SSTL15 | VCCAUX_IO = NORMAL;

NET "ddr3_addr[2]" LOC = "AD8" | IOSTANDARD = SSTL15 | VCCAUX_IO = NORMAL;

NET "ddr3_addr[3]" LOC = "AF7" | IOSTANDARD = SSTL15 | VCCAUX_IO = NORMAL;

NET "ddr3_addr[4]" LOC = "AC11" | IOSTANDARD = SSTL15 | VCCAUX_IO = NORMAL;

NET "ddr3_addr[5]" LOC = "AC8" | IOSTANDARD = SSTL15 | VCCAUX_IO = NORMAL;

NET "ddr3_addr[6]" LOC = "Y10" | IOSTANDARD = SSTL15 | VCCAUX_IO = NORMAL;

NET "ddr3_addr[7]" LOC = "V8" | IOSTANDARD = SSTL15 | VCCAUX_IO = NORMAL;

NET "ddr3_addr[8]" LOC = "AA7" | IOSTANDARD = SSTL15 | VCCAUX_IO = NORMAL;

NET "ddr3_addr[9]" LOC = "AB7" | IOSTANDARD = SSTL15 | VCCAUX_IO = NORMAL;

NET "ddr3_ba[0]" LOC = "W9" | IOSTANDARD = SSTL15 | VCCAUX_IO = NORMAL;

NET "ddr3_ba[1]" LOC = "AB11" | IOSTANDARD = SSTL15 | VCCAUX_IO = NORMAL;

NET "ddr3_ba[2]" LOC = "W8" | IOSTANDARD = SSTL15 | VCCAUX_IO = NORMAL;

NET "ddr3_cas_n" LOC = "W10" | IOSTANDARD = SSTL15 | VCCAUX_IO = NORMAL;

NET "ddr3_ck_n[0]" LOC = "AB9" | IOSTANDARD = DIFF_SSTL15 | VCCAUX_IO = NORMAL;

NET "ddr3_ck_p[0]" LOC = "AA9" | IOSTANDARD = DIFF_SSTL15 | VCCAUX_IO = NORMAL;

NET "ddr3_cke[0]" LOC = "AB10" | IOSTANDARD = SSTL15 | VCCAUX_IO = NORMAL;

NET "ddr3_cs_n[0]" LOC = "Y8" | IOSTANDARD = SSTL15 | VCCAUX_IO = NORMAL;

NET "ddr3_dm[0]" LOC = "AD16" | IOSTANDARD = SSTL15 | VCCAUX_IO = NORMAL;

NET "ddr3_dm[1]" LOC = "AB16" | IOSTANDARD = SSTL15 | VCCAUX_IO = NORMAL;

NET "ddr3_dm[2]" LOC = "AD18" | IOSTANDARD = SSTL15 | VCCAUX_IO = NORMAL;

NET "ddr3_dm[3]" LOC = "V14" | IOSTANDARD = SSTL15 | VCCAUX_IO = NORMAL;

NET "ddr3_dq[0]" LOC = "AF14" | IOSTANDARD = SSTL15_T_DCI | VCCAUX_IO = NORMAL;

NET "ddr3_dq[10]" LOC = "AA18" | IOSTANDARD = SSTL15_T_DCI | VCCAUX_IO = NORMAL;

NET "ddr3_dq[11]" LOC = "AA14" | IOSTANDARD = SSTL15_T_DCI | VCCAUX_IO = NORMAL;

NET "ddr3_dq[12]" LOC = "AD14" | IOSTANDARD = SSTL15_T_DCI | VCCAUX_IO = NORMAL;

NET "ddr3_dq[13]" LOC = "AB14" | IOSTANDARD = SSTL15_T_DCI | VCCAUX_IO = NORMAL;

NET "ddr3_dq[14]" LOC = "AA17" | IOSTANDARD = SSTL15_T_DCI | VCCAUX_IO = NORMAL;

NET "ddr3_dq[15]" LOC = "AA15" | IOSTANDARD = SSTL15_T_DCI | VCCAUX_IO = NORMAL;

NET "ddr3_dq[16]" LOC = "AB17" | IOSTANDARD = SSTL15_T_DCI | VCCAUX_IO = NORMAL;

NET "ddr3_dq[17]" LOC = "AB19" | IOSTANDARD = SSTL15_T_DCI | VCCAUX_IO = NORMAL;

NET "ddr3_dq[18]" LOC = "AC17" | IOSTANDARD = SSTL15_T_DCI | VCCAUX_IO = NORMAL;

NET "ddr3_dq[19]" LOC = "AA20" | IOSTANDARD = SSTL15_T_DCI | VCCAUX_IO = NORMAL;

NET "ddr3_dq[1]" LOC = "AF17" | IOSTANDARD = SSTL15_T_DCI | VCCAUX_IO = NORMAL;

NET "ddr3_dq[20]" LOC = "AC18" | IOSTANDARD = SSTL15_T_DCI | VCCAUX_IO = NORMAL;

NET "ddr3_dq[21]" LOC = "AA19" | IOSTANDARD = SSTL15_T_DCI | VCCAUX_IO = NORMAL;

NET "ddr3_dq[22]" LOC = "AC19" | IOSTANDARD = SSTL15_T_DCI | VCCAUX_IO = NORMAL;

NET "ddr3_dq[23]" LOC = "AD19" | IOSTANDARD = SSTL15_T_DCI | VCCAUX_IO = NORMAL;

NET "ddr3_dq[24]" LOC = "Y17" | IOSTANDARD = SSTL15_T_DCI | VCCAUX_IO = NORMAL;

NET "ddr3_dq[25]" LOC = "V16" | IOSTANDARD = SSTL15_T_DCI | VCCAUX_IO = NORMAL;

NET "ddr3_dq[26]" LOC = "V19" | IOSTANDARD = SSTL15_T_DCI | VCCAUX_IO = NORMAL;

NET "ddr3_dq[27]" LOC = "W16" | IOSTANDARD = SSTL15_T_DCI | VCCAUX_IO = NORMAL;

NET "ddr3_dq[28]" LOC = "V17" | IOSTANDARD = SSTL15_T_DCI | VCCAUX_IO = NORMAL;

NET "ddr3_dq[29]" LOC = "W14" | IOSTANDARD = SSTL15_T_DCI | VCCAUX_IO = NORMAL;

NET "ddr3_dq[2]" LOC = "AE15" | IOSTANDARD = SSTL15_T_DCI | VCCAUX_IO = NORMAL;

NET "ddr3_dq[30]" LOC = "V18" | IOSTANDARD = SSTL15_T_DCI | VCCAUX_IO = NORMAL;

NET "ddr3_dq[31]" LOC = "W15" | IOSTANDARD = SSTL15_T_DCI | VCCAUX_IO = NORMAL;

NET "ddr3_dq[3]" LOC = "AE17" | IOSTANDARD = SSTL15_T_DCI | VCCAUX_IO = NORMAL;

NET "ddr3_dq[4]" LOC = "AD15" | IOSTANDARD = SSTL15_T_DCI | VCCAUX_IO = NORMAL;

NET "ddr3_dq[5]" LOC = "AF20" | IOSTANDARD = SSTL15_T_DCI | VCCAUX_IO = NORMAL;

NET "ddr3_dq[6]" LOC = "AF15" | IOSTANDARD = SSTL15_T_DCI | VCCAUX_IO = NORMAL;

NET "ddr3_dq[7]" LOC = "AF19" | IOSTANDARD = SSTL15_T_DCI | VCCAUX_IO = NORMAL;

NET "ddr3_dq[8]" LOC = "AB15" | IOSTANDARD = SSTL15_T_DCI | VCCAUX_IO = NORMAL;

NET "ddr3_dq[9]" LOC = "AC14" | IOSTANDARD = SSTL15_T_DCI | VCCAUX_IO = NORMAL;

NET "ddr3_dqs_n[0]" LOC = "AF18" | IOSTANDARD = DIFF_SSTL15_T_DCI | VCCAUX_IO = NORMAL;

NET "ddr3_dqs_n[1]" LOC = "Y16" | IOSTANDARD = DIFF_SSTL15_T_DCI | VCCAUX_IO = NORMAL;

NET "ddr3_dqs_n[2]" LOC = "AE20" | IOSTANDARD = DIFF_SSTL15_T_DCI | VCCAUX_IO = NORMAL;

NET "ddr3_dqs_n[3]" LOC = "W19" | IOSTANDARD = DIFF_SSTL15_T_DCI | VCCAUX_IO = NORMAL;

NET "ddr3_dqs_p[0]" LOC = "AE18" | IOSTANDARD = DIFF_SSTL15_T_DCI | VCCAUX_IO = NORMAL;

NET "ddr3_dqs_p[1]" LOC = "Y15" | IOSTANDARD = DIFF_SSTL15_T_DCI | VCCAUX_IO = NORMAL;

NET "ddr3_dqs_p[2]" LOC = "AD20" | IOSTANDARD = DIFF_SSTL15_T_DCI | VCCAUX_IO = NORMAL;

NET "ddr3_dqs_p[3]" LOC = "W18" | IOSTANDARD = DIFF_SSTL15_T_DCI | VCCAUX_IO = NORMAL;

NET "ddr3_odt[0]" LOC = "AD9" | IOSTANDARD = SSTL15 | VCCAUX_IO = NORMAL;

NET "ddr3_ras_n" LOC = "AA8" | IOSTANDARD = SSTL15 | VCCAUX_IO = NORMAL;

NET "ddr3_reset_n" LOC = "AF10" | IOSTANDARD = LVCMOS15 | VCCAUX_IO = NORMAL;

NET "ddr3_we_n" LOC = "AF9" | IOSTANDARD = SSTL15 | VCCAUX_IO = NORMAL;

时钟管脚

CLK 50M <-> G22

CLK 74.25M <-> E18

CLK 差分125M P <-> D6

CLK 差分125M N <-> D5

LED

LVCMOS33高电平点亮

D1-1 <-> A23

D1-2 <-> A24

D2-1 <-> D23

D2-2 <-> C24

D3-1 <-> C26

D3-2 <-> D24

D4-1 <-> D25

D4-2 <-> E25

按键

按下为低电平

KEY1 <-> D26

KEY2 <-> G25

KEY3 <-> E26

KEY4 <-> G26

KEY5 <-> H26

USB UART

CH340_Rx <-> A17

CH340_Tx <-> B17

TF卡座

CLK <-> E23

CMD <-> G24

D0 <-> F23

D1 <-> F22

D2 <-> F25

D3 <-> F24

EEPROM 24C02

FPGA_I2C_SDA <-> C21

FPGA_I2C_SCL3 <-> B21

HDMI1 OUT TMDS33 P

tmds_data_p[0] <-> AF24

tmds_data_p[1] <-> AE23

tmds_data_p[2] <-> AC23

tmds_clk_p <-> AB21

tmds_oen <-> AE22 LVCMOS33

商品页面图