简介

LCD1602显示驱动模组是使用System verilog编写的IP核,适用于FPGA,可以自动完成初始化,刷屏等工作。使用者仅需要像读写SRAM一样向显示存储器写入数据,LCD1602就能显示出对应的字符。

FPGA实机效果展示

端口功能

例化参数CLK_F设置为输入时钟频率,单位为Hz。例如,输入5MHz时钟,CLK_F设置为5_000_000。

内部高速逻辑交互

| 方向 | 名称 | 功能 |

|---|---|---|

| 输入 | clk | 时钟输入 |

| 输入 | rst_n | 低电平复位 |

| 输入 | addr | [4:0]显示存储器的地址,上升沿采样 |

| 输入 | din | [7:0]显示存储器数据输入,上升沿采样 |

| 输出 | dout | [7:0]显示存储器数据输出,上升沿后输出 |

| 输入 | we | 显示存储器写入使能,高电平有效,上升沿采样 |

显示存储器的交互逻辑为同步读写,操作方式类似FPGA中的BRAM。

- 写操作:在时钟上升沿来临前,准备好:写地址addr,写数据din,we=1;上升沿完成写入

- 读操作:在时钟上升沿来临前,准备好:读地址addr,we=0;上升沿后在dout端口输出

外部交互,连接LCD1602

| 方向 | 名称 | 功能 |

|---|---|---|

| 双向 | DB | 连接LCD1602 |

| 输出 | RS | 连接LCD1602 |

| 输出 | RW | 连接LCD1602 |

| 输出 | EN | 连接LCD1602 |

显示配置

addr[4:0]有5个地址线,可以寻址32个8位的存储空间。每个存储空间依次对应LCD1602的两行32个字符.映射关系为addr=(行-1)*16+(列-1)

例如:1602的第一行第3列,对应地址为(1-1)*16+(3-1)=2。第二行第1列,对应地址为(2-1)*16+(1-1)=16

向某个地址写入ASCII码,就能在1602上的对应位置显示出对应的字符。

仿真

本工程仿真环境基于iverilog,且版本必须>=11。

首先,进入RTL/tb文件夹。

linux:

终端输入make执行仿真,make clean清理文件。

windows:

双击make.bat执行仿真。

双击clean.bat清理文件。

原理描述

LCD1602显示驱动模组由两层状态机构成。高层状态机是刷屏状态机,负责1602初始化、行切换、字符写入;低层状态机是写操作状态机,负责控制具体的读写时序,完成判忙、数据/指令写入。

两层状态机都是Moore型状态机,输出只与当前状态有关。

dram是一个8*32的显示存储器,每一个字节与LCD1602显示屏的一个格子对应。其中,dram[0]至[15]对应LCD1602第一行从左到右16个格子,dram[16]至[31]对应LCD1602第二行从左到右16个格子。

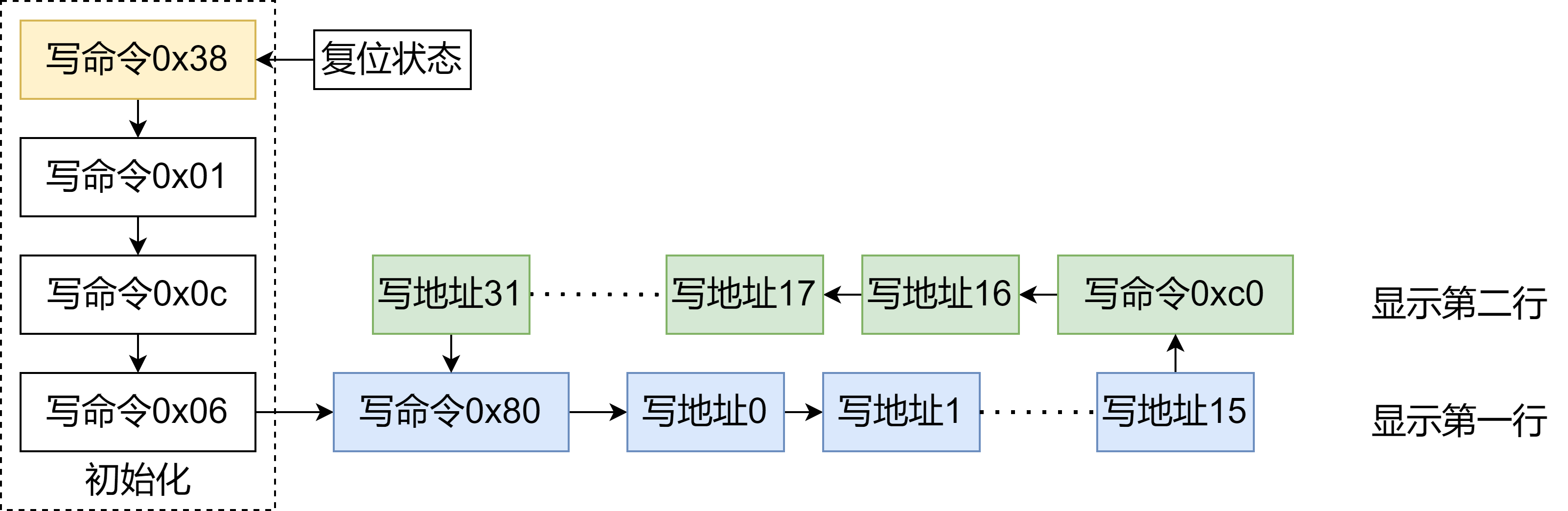

刷屏状态机

写命令0x38是状态机的复位状态,从写命令0x38到0x06是LCD1602复位流程,只会执行一次。

写命令0x38是状态机的复位状态,从写命令0x38到0x06是LCD1602复位流程,只会执行一次。

写命令0x80状态将LCD1602的ddram指针指向显示屏的第一行行首。之后,将dram[0]至dram[15]的数据逐个写入LCD1602的ddram。

写命令0xc0状态将LCD1602的ddram指针指向显示屏的第二行行首。之后,将dram[16]至dram[31]的数据逐个写入LCD1602的ddram。

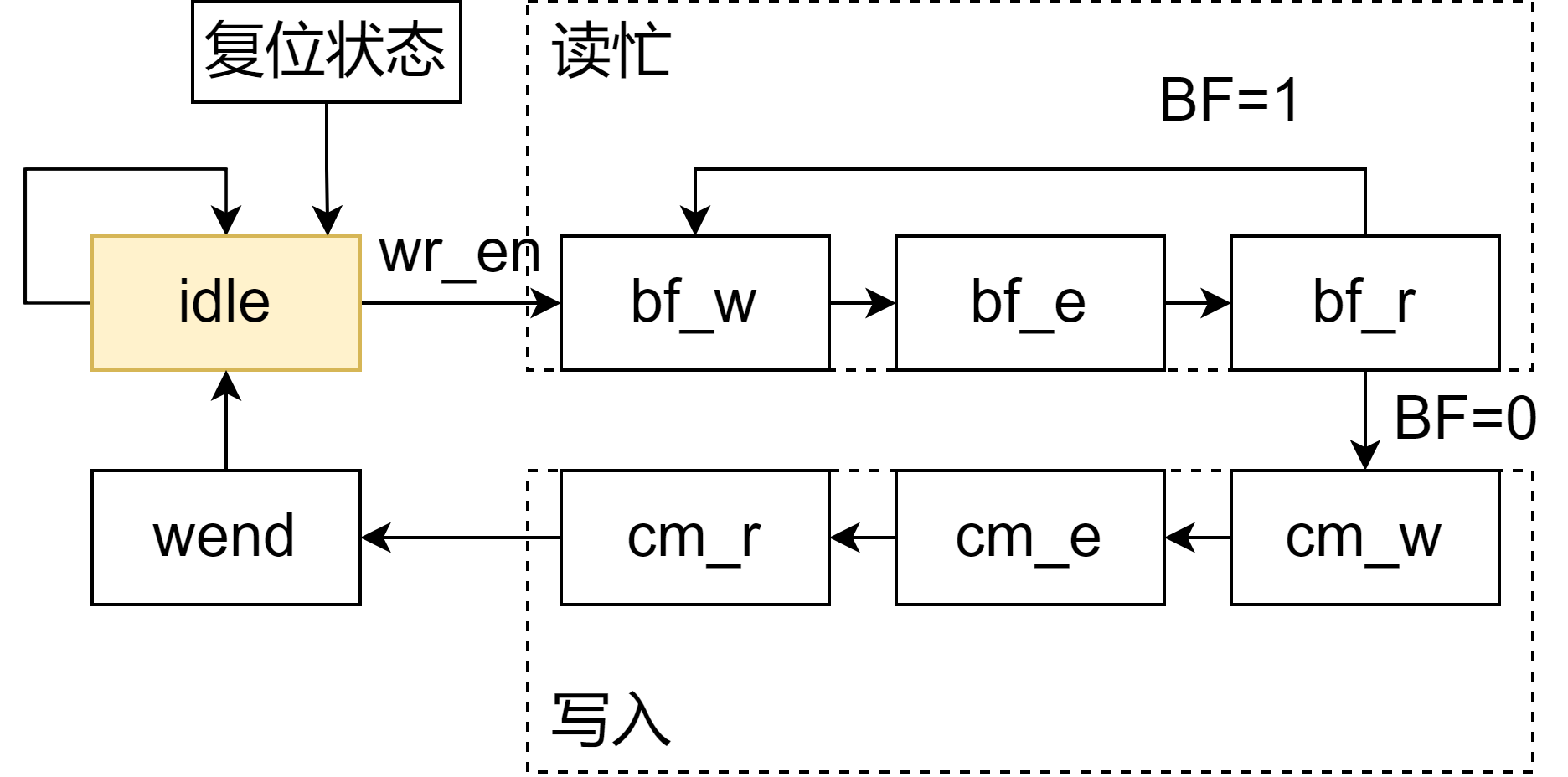

写操作状态机

idle是状态机的复位状态,此状态什么都不会做。

idle是状态机的复位状态,此状态什么都不会做。

当wr_en被拉高,会由idle进入写操作流程。

在写操作前,需要读取一次命令,检查BF位是否为0。如果BF=0,继续写操作,如果BF=1,则再次读取命令。

写操作和读命令都需要3个状态,分别是设置控制线,EN拉高,EN拉低,具体操作由刷屏状态机传递的参数决定。