简介

逐次逼近型SAR ADC广泛应用于各种嵌入式处理器,其结构特性决定了它在14bit 1MSPS以下具有成本优势。

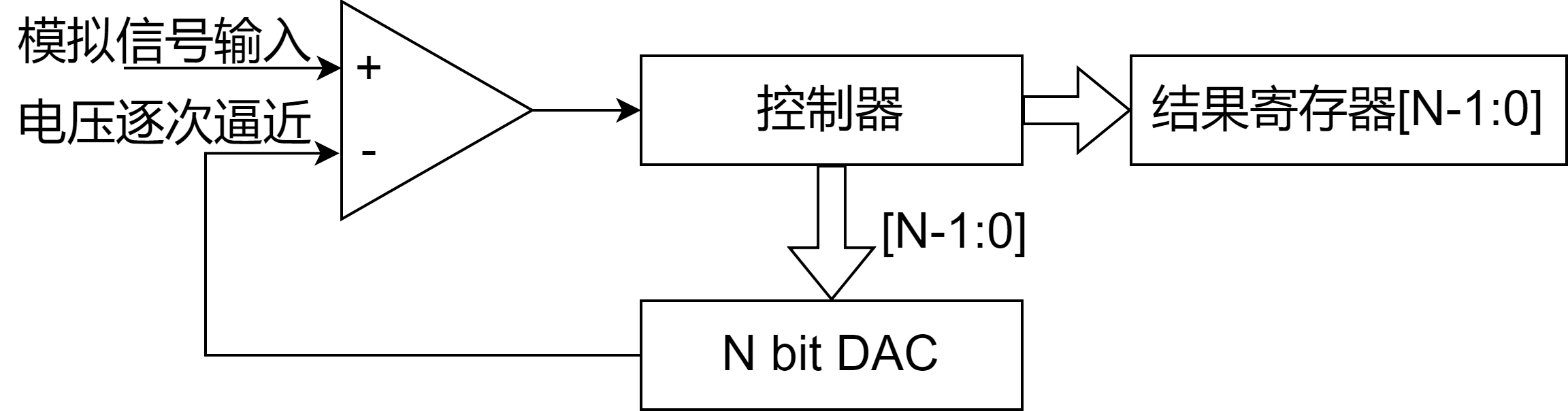

SAR ADC由比较器,DAC数模转换,控制单元,比较寄存器构成。启动转换后,比较器会将输入信号和DAC反馈进行比较,从高位开始,1个时钟周期完成一次比较,让DAC的输出电压逐次逼近输入信号,N bit ADC一次转换需要N个时钟周期。转换完成后,输出一个二进制数。

转换过程

逐次逼近型ADC最大的特点体现在逐次逼近。

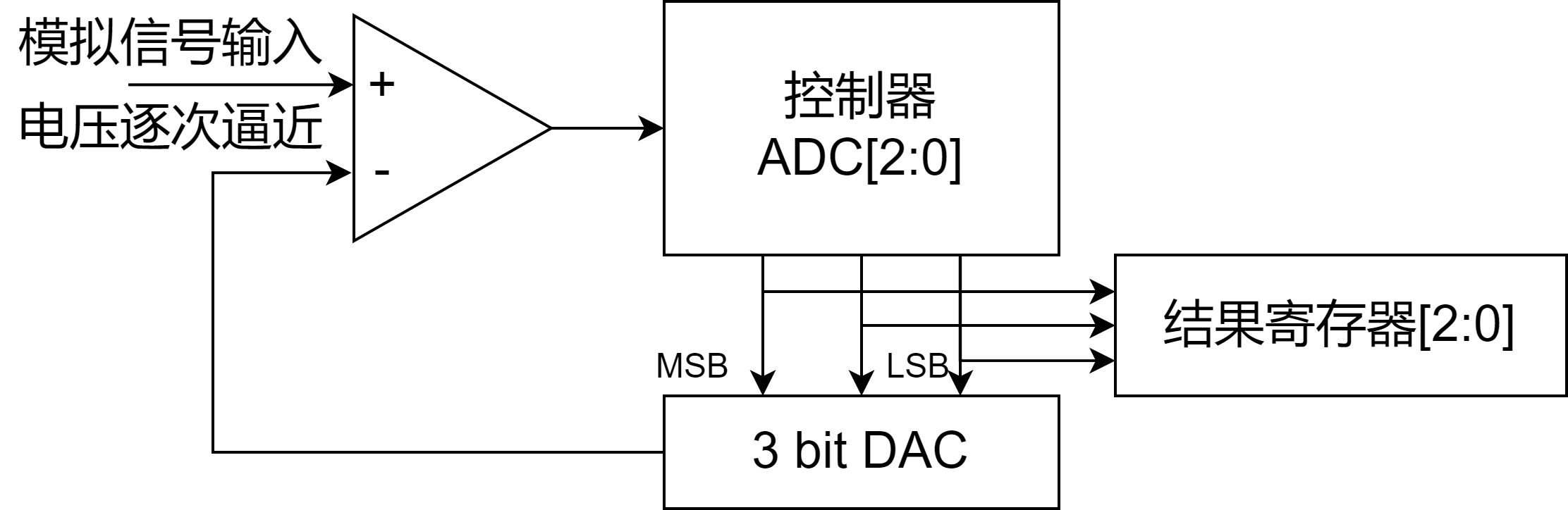

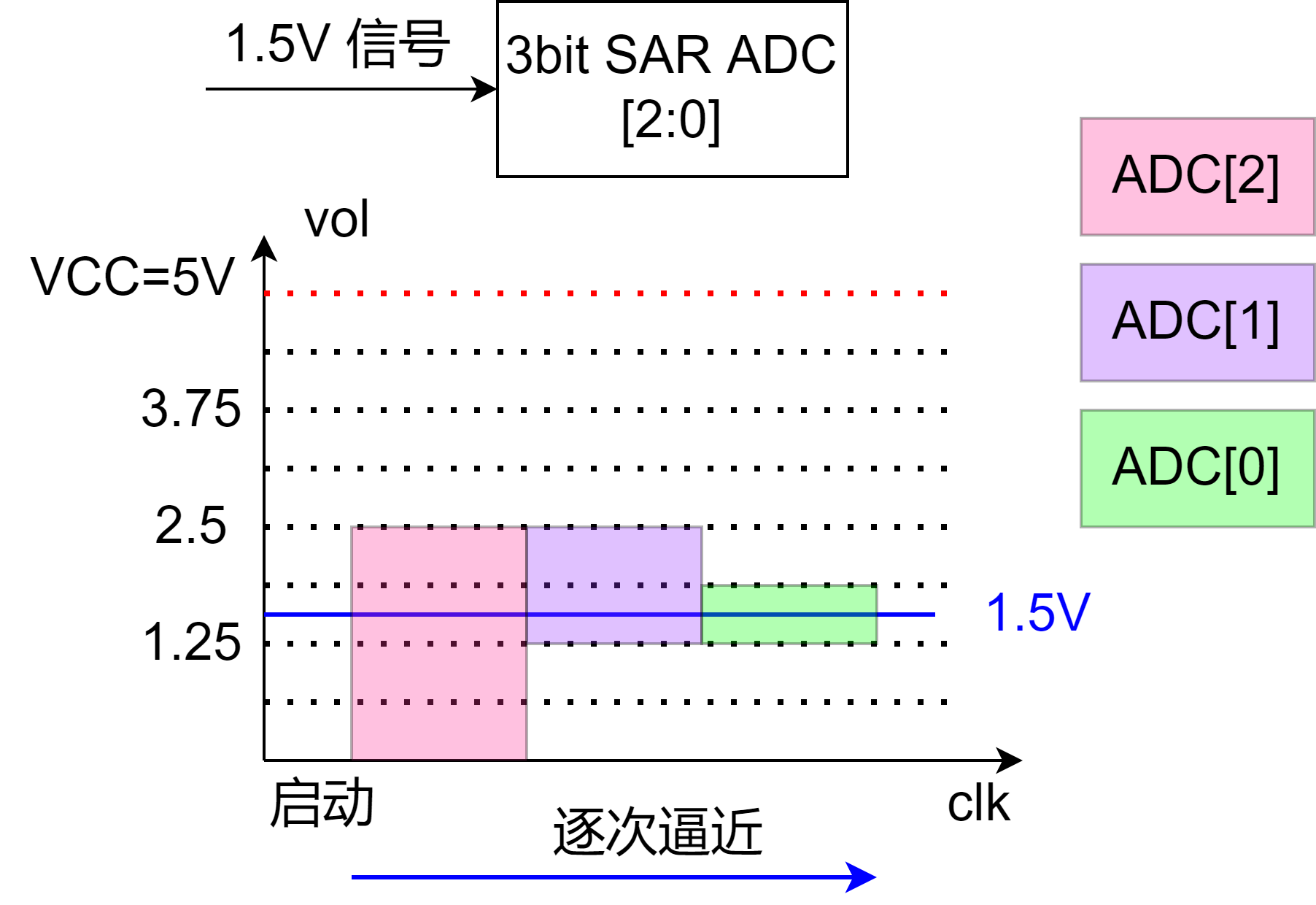

如图,以一个3bit SAR ADC为例,它的比较寄存器ADC[2:0]有3位,参考电压为5V。也就是说,一个0-5V的模拟信号通过ADC,将会被转换成000-111的数字信号,分辨率为0.625V,并且转换需要3个周期。

启动转换后,控制器将会从最高位ADC[2]开始比较,DAC逐次逼近输入的1.5V,直到完成ADC[0]的转换。

启动转换后,控制器将会从最高位ADC[2]开始比较,DAC逐次逼近输入的1.5V,直到完成ADC[0]的转换。

首先,比较最高位ADC[2],对应图片的粉色方块部分。DAC输出100,对应电压2.5V,大于1.5V,ADC[2]赋值为0

首先,比较最高位ADC[2],对应图片的粉色方块部分。DAC输出100,对应电压2.5V,大于1.5V,ADC[2]赋值为0

其次,比较ADC[1],对应图片的紫色方块部分。由于ADC[2]==0,因此DAC输出010,对应电压0+1.25V,小于1.5V,ADC[1]赋值为1

最后,比较ADC[0],对应图片的绿色方块部分。由于ADC[2:1]==01,因此DAC输出011,对应电压0+1.25+0.625V,大于1.5V,ADC[0]赋值为0

至此,SAR ADC转换完成,输出数字量ADC[2:0]=010=2,输入信号/分辨率1.5/0.625=2.4,结果符合预期。

仿真

本工程仿真环境基于iverilog,且版本必须>=11。

首先,进入RTL/tb文件夹。

-

linux:

终端输入make执行仿真,make clean清理文件。 -

windows:

进入tb文件夹,双击make.bat执行仿真。

清理文件,双击clean.bat。