介绍

- 工程基于lattice提供的方案。

lattice提供的方案 - 本工程致力于以下两个目标:

- 使用实例帮助初学者理解Σ-Δ(Sigma-Delta)ADC的原理

- 在FPGA上使用简单的外围电路,实现AD转换

- 实现所需的器件

- 一个运放或比较器

- 电容电阻

- 一个FPGA

系统架构

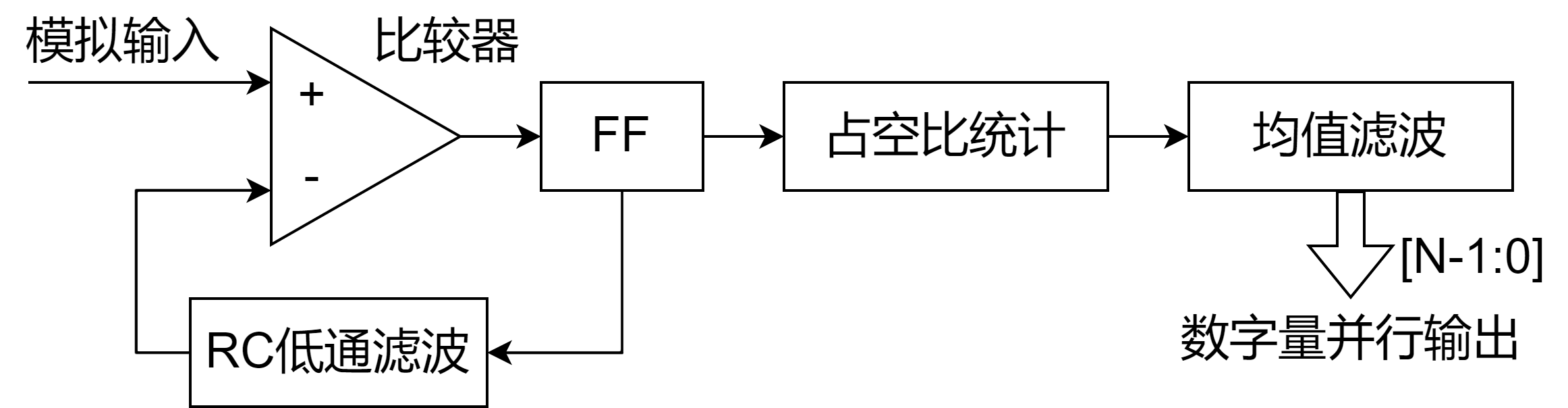

逻辑结构

Σ-Δ ADC一眼看上去,都看不出能AD转换,给人一种“这真的是ADC吗”的感觉。

本人才疏学浅,大神讲解得更深入:B站链接

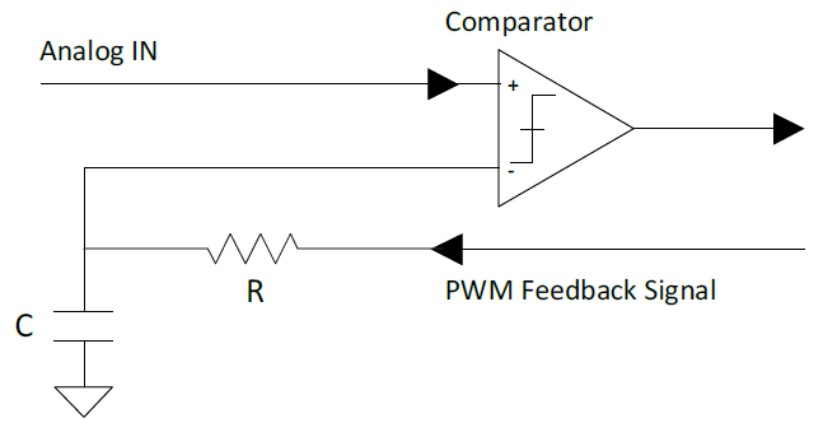

外围电路

显而易见,这是一个比较器,或者是一个工作在比较器状态的运放。

模拟信号连接至正相输入端,反馈信号经过RC滤波连接至反相输入端,比较器输出连接至FPGA。

RC滤波器是一个低通滤波器,截止频率与ADC的采样速率和FPGA工作频率有关。

数字设计

外围电路将模拟信号转换为1位的01序列,这样我们就能用数字逻辑去处理模拟信号。

- 使用一个累加器,统计一段固定长度序列中1的个数。通过这种方法,可以将01序列转换为一段序列的占空比。累加器宽度由ACCUM_BITS决定。

- 占空比信号是有波动的,后端使用一个均值滤波器去除毛刺,滤波器越深,信号速率越低,精度越高。滤波器深度由LPF_DEPTH_BITS决定。

- ADC_WIDTH参数贯穿始终,它是ADC的位宽。

使用教程

逻辑仿真

windows环境,需要安装iverilog。

clone项目,进入RTL/tb,运行make.bat制作实物

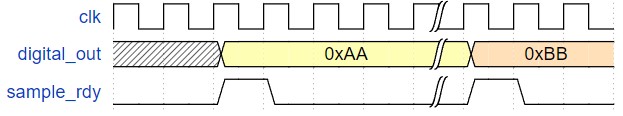

k7_fpga.rar是vivado 2019.2的工程,配合

硬件电路/提供的原理图,可以实现Σ-Δ ADC。输出时序

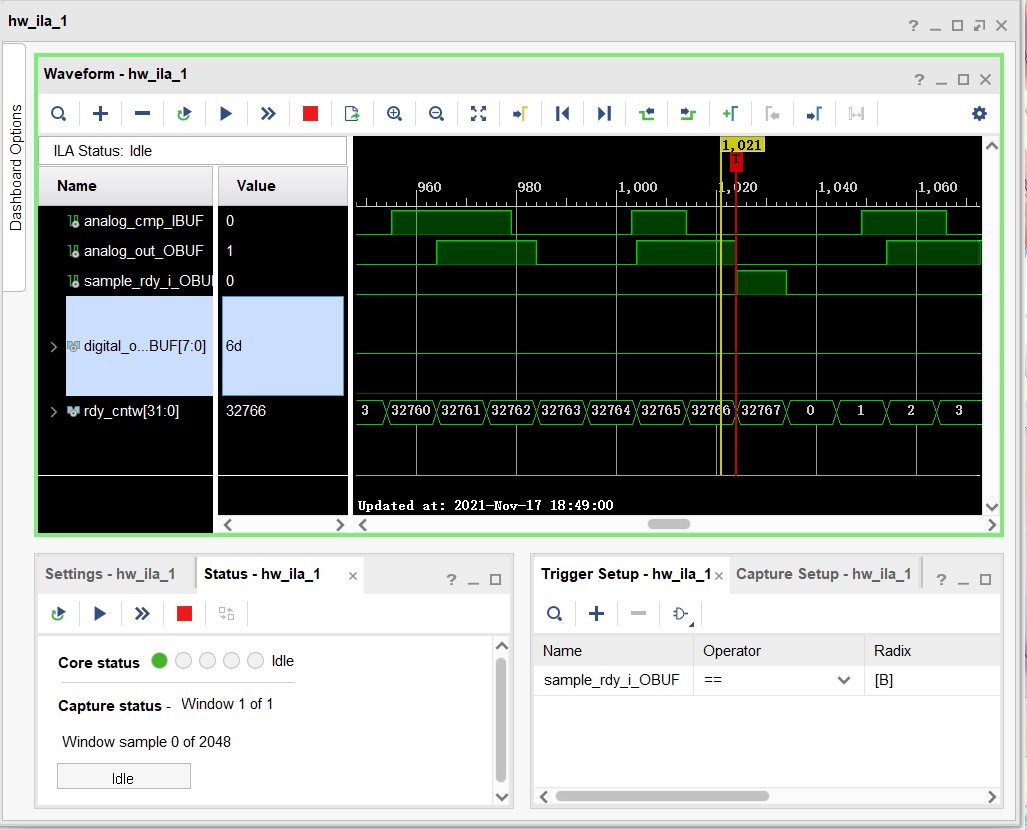

演示

使用7k325连接外围电路,采集电压,8bit输出。内置逻辑分析仪查看情况。

sample_rdy高电平脉冲表示一次转换结束,输出结果为0x6d。

实验的ADC位宽为8bit,量程是0-3.3V,那么实际电压为0x6d/0xff*3.3=1.41v,与万用表测量结果吻合。